# System Power Supply IC with Connunication Function (Master Type) BD9400BFP

## •Description

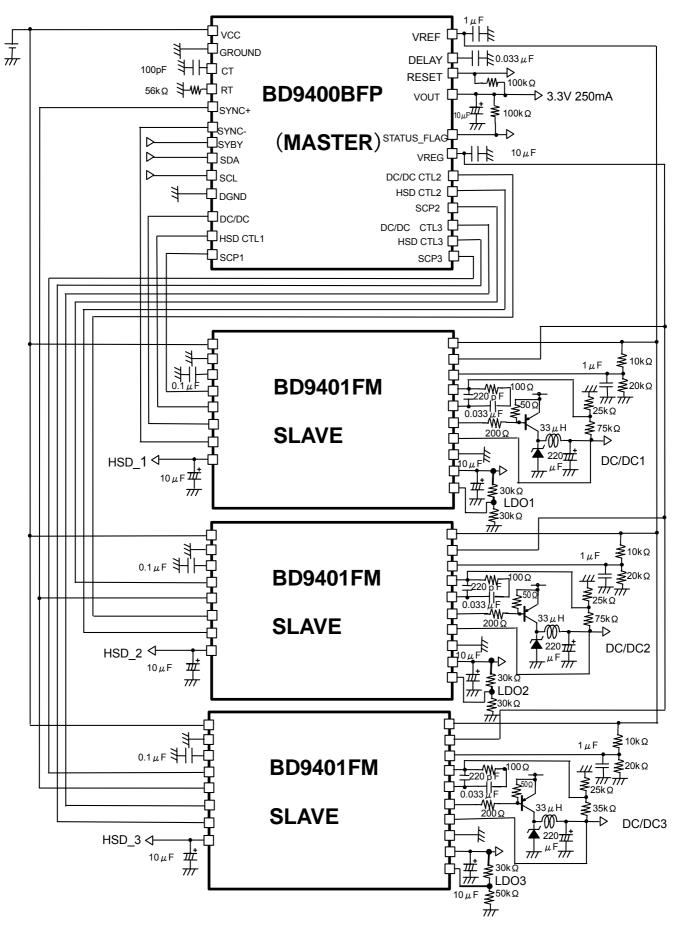

The BD9400BFP can be combined with the BD9401FM/BD9403FV to create application-specific system power supplies. It can be controlled using an I<sup>2</sup>C BUS. The BD9400BFP is a main control chip featuring an I<sup>2</sup>C BUS bidirectional communications function, a VDD LDO (for microcontroller use), a VDD reset, and BD9401FM/BD9403FV control circuits. The IC's I<sup>2</sup>C BUS communications function allows switching regulator and high-side switch on/off control, as well as switching regulator frequency adjustment, using a maximum of 3 channels. The I<sup>2</sup>C BUS read function can be used to send power supply overvoltage and undervoltage detection signals, as well as switching regulator output short detection signals.

#### Features

- 1) The IC can be combined with the BD9401FM/BD9403FV to provide design flexibility.

- 2) On/off control of up to 6 outputs with I<sup>2</sup>C BUS control

- 3) Broad input voltage range: 7 V to 36 V

- 4) Built-in LDO regulator for use with microcontrollers

- 5) LDO regulator: 3.3 V, 250 mA (±2% precision)

- 6) Built-in regulator voltage detection reset circuit

- 7) Built-in power supply overvoltage and undervoltage detection circuits

- 8) Dual reference voltage sources for BD9401FM/BD9403FV (VREF, VREG), and built-in triangular waveform oscillator

- 9) VREF reference voltage precision: ±1%

- 10) The triangular waveform oscillator frequency can be changed to  $\pm 10\%$  or  $\pm 20\%$  using I<sup>2</sup>C BUS control.

- 11) Flag output for undervoltage detection, overvoltage detection, and BD9401FM/BD9403FV short protection detection signals

- 12) Total system stand-by current of 60 μA (Typ.) when VDDLDO, reset, overvoltage, and undervoltage detection circuits are set.

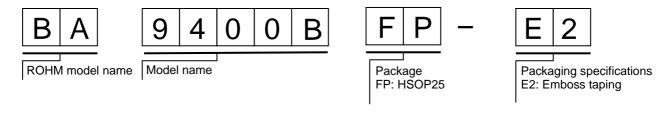

- 13) Package: HSOP25

## Applications

Car audio, satellite navigation systems, etc.

#### • Absolute maximum ratings (Ta = 25°C)

| Parameter                    | Symbol         | Limit              | Unit |

|------------------------------|----------------|--------------------|------|

| Power supply voltage         | Vcc            | 36 <sup>*1</sup>   | V    |

| Applied voltage              | SDA, SCL, STBY | 7                  | V    |

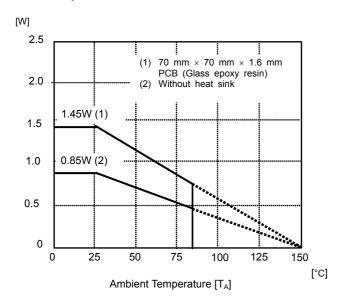

| Power dissipation 1          | P01            | 0.85 <sup>*2</sup> | W    |

| Power dissipation 2          | P02            | 1.45 <sup>*3</sup> | W    |

| Operating temperature range  | Topr           | -40 to +85         | °C   |

| Storage temperature range    | Тѕтс           | +150               | °C   |

| Maximum junction temperature | Тјмах          | +150               | °C   |

\*1 Not to exceed Pd.

\*2 Reduced by 6.8 mW/°C over Ta  $\geq$  25°C during IC without heat sink operation.

\*3 Reduced by 11.6 mW/°C over Ta  $\geq$  25°C, when mounted on a glass epoxy board (70.0 mm  $\times$  70.0 mm  $\times$  1.6 mm).

#### ●Recommended operating ranges (Ta = 25°C) (Not to exceed Pd.)

| Parameter                              | Symbol | Min. | Max. | Unit |

|----------------------------------------|--------|------|------|------|

| Power supply voltage                   | Vcc    | 8    | 26   | V    |

| Oscillating frequency (PWM controller) | fosc   | 30   | 500  | KHz  |

#### ●Electrical characteristics (Unless otherwise specified, Ta = 25°C; Va = 13.5 V; STDY = 3.3 V)

| Deventer                                      | Oursels al           |      | Limit |      | 1.1  | Quartitions                                         |

|-----------------------------------------------|----------------------|------|-------|------|------|-----------------------------------------------------|

| Parameter                                     | Symbol               | Min. | Тур.  | Max. | Unit | Conditions                                          |

| [Oscillator block]                            |                      |      |       |      |      |                                                     |

| Oscillating frequency                         | Fosc                 | 162  | 180   | 198  | KHz  | CT = 1000PF, RT = 52 kΩ                             |

| Frequency Va fluctuation                      | IROSC                |      |       | 2    | %    | Vcc = 8 V to 25V                                    |

| Frequency rate of change 1                    | ∆Fosc1               |      | +10   |      | %    | Compliant with I <sup>2</sup> C BUS specifications. |

| Frequency rate of change 2                    | ∆Fosc2               | —    | -10   | —    | %    | Compliant with I <sup>2</sup> C BUS specifications. |

| Frequency rate of change 3                    | ∆Fosc3               |      | +20   | _    | %    | Compliant with I <sup>2</sup> C BUS specifications. |

| Frequency rate of change 4                    | ∆Fosc4               | —    | -20   | —    | %    | Compliant with I <sup>2</sup> C BUS specifications. |

| [Reference voltage]                           |                      |      |       |      |      |                                                     |

| Output voltage                                | VREF                 | 2.97 | 3.00  | 3.03 | V    | lo = 1 mA                                           |

| Line regulation                               | $\Delta REF1$        | —    | 1     | 10   | mV   | Vcc = 8 V to 26 V                                   |

| Load regulation                               | $\Delta \text{REF0}$ | —    | 5     | 20   | mV   | lo = 1 mA                                           |

| Short current                                 | IOVREF               | —    | 30    | —    | mA   |                                                     |

| [VREG voltage]                                | 1                    |      |       |      | i    | ,                                                   |

| Output voltage                                | Vreg                 | 4.5  | 5.0   | 5.5  | V    | lo = 0 mA                                           |

| Output current capacity                       | IREG                 | 10   | —     | —    | mA   |                                                     |

| [Standby control]                             |                      |      |       |      |      |                                                     |

| On mode voltage                               | VSTAH                | 2.3  | —     | 3.3  | V    |                                                     |

| Off mode voltage                              | VSTAL                | 0    | —     | 1.0  | V    |                                                     |

| [Overall]                                     |                      |      |       |      |      |                                                     |

| Total supply current                          | loc                  |      | 1.0   | 2.0  | mA   | Vst = 3.3 V                                         |

| Total supply current during standby operation | ISTBY                | —    | 60    | 100  | μA   | VSTB = 0 V                                          |

#### •Electrical characteristics

| Parameter                      | C: make al    |       | Limit |       | Unit | Conditions                       |  |

|--------------------------------|---------------|-------|-------|-------|------|----------------------------------|--|

| Parameter                      | Symbol        | Min.  | Тур.  | Max.  | Unit | Conditions                       |  |

| [Output voltage 3.3 V, 250 mA] |               |       |       |       |      |                                  |  |

| Output voltage                 | Vo            | 3.234 | 3.3   | 3.366 | V    | lo = 10 mA                       |  |

| Output peak current            | IPEAK         | 0.25  | —     | 2     | А    |                                  |  |

| Line regulation                | $\Delta VOL$  | _     | 10    | 20    | mV   | Vcc = 9 V to 26 V, Io = 10 mA    |  |

| Load regulation                | $\Delta V OR$ | _     | 30    | 60    | mV   | lo = 10 mA to 200 mA             |  |

| Ripple rejection               | RR            | 50    | 60    | _     | dB   | F = 100 Hz, 0.5 VP-P, lo = 10 mA |  |

| [RESET]                        |               |       |       |       |      |                                  |  |

| Detection voltage              | Vdr           | 2.66  | 2.80  | 2.94  | V    |                                  |  |

| Hysteresis voltage             | $\Delta DR$   | _     | 90    | _     | mV   |                                  |  |

| Delay time                     | TDR           | 5     | 10    | 20    | ms   | CDELAY = 0.01 UF                 |  |

| [Overvoltage detection]        |               |       |       |       |      |                                  |  |

| Detection voltage              | Vdo           | 17.5  | 18.5  | 19.5  | V    | lo = 0 mA                        |  |

| Hysteresis voltage             | Δdo           | _     | 400   | _     | mV   |                                  |  |

| [Reduced-voltage detection]    |               |       |       |       |      |                                  |  |

| Detection voltage              | Vdu           | 8.0   | 8.5   | 9.0   | V    |                                  |  |

| Hysteresis voltage             | ΔDU           | _     | 150   | _     | mV   |                                  |  |

| [STATUS_FLAG]                  |               |       |       |       |      |                                  |  |

| Output current capacity        | ISTF          | 1     | _     | _     | mA   | VSTASTUS_FLAG = 0.4 V            |  |

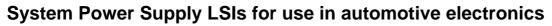

## •I<sup>2</sup>C BUS specifications

(1) BUS line and I/O timing and electrical characteristics

Fig.1 I<sup>2</sup>C BUS Timing Definitions

## Table A: I<sup>2</sup>C BUS Device SDA, SCL BUS Line Characteristics

| Parameter                                                       | Symbol   |      | Standard mode<br>I <sup>2</sup> C BUS |     |  |

|-----------------------------------------------------------------|----------|------|---------------------------------------|-----|--|

|                                                                 |          | Min. | Max.                                  |     |  |

| SCL frequency                                                   | fSCL     | 0    | 100                                   | KHz |  |

| Stop/start condition open time                                  | tBUF     | 4.7  | _                                     | Ms  |  |

| Start condition (when repeating)                                | HUD: STA | 4.0  |                                       |     |  |

| The minimum clock pulse is generated after this period elapses. | tHD;STA  | 4.0  | _                                     | μS  |  |

| SCL clock low interval                                          | tLOW     | 4.7  | —                                     | μS  |  |

| SCL clock high interval                                         | tHIGH    | 4.0  | —                                     | μS  |  |

| Start condition setup time when repeating                       | tSU;STA  | 4.7  | _                                     | μS  |  |

| Hold time                                                       | tHD;DAT  | 0*   | —                                     | μS  |  |

| Setup time                                                      | tSU;DAT  | 250  | _                                     | NS  |  |

| SDA and SCL rise time                                           | tR       | _    | 1000                                  | NS  |  |

| SDA and SCL fall time                                           | tF       | _    | 300                                   | NS  |  |

| Stop condition setup time                                       | tSU;STO  | 4.0  | _                                     | μS  |  |

| BUS line allowable capacitance value                            | Cb       |      | 400                                   | pF  |  |

Note: All values comply with minimum VIH and maximum VLL levels (Table B).

\* A minimum hold time of 300 ns must be provided to ensure that the region for which the device's SCL falling edge is not defined is exceeded.

Table B: I<sup>2</sup>C BUS Device SDA and SCL I/O Stage Characteristics

| Parameter                                                           | Symbol | Standaro<br>I <sup>2</sup> C E |                   | Unit |  |

|---------------------------------------------------------------------|--------|--------------------------------|-------------------|------|--|

|                                                                     |        | Min.                           | Max.              |      |  |

| Low level input voltage                                             |        |                                |                   |      |  |

| Fixed input level                                                   | VIL    | -0.5                           | 0.6               | V    |  |

| (VDD-dependent input level)                                         |        | (-0.5)                         | (0.2VDD)          |      |  |

| High level input voltage                                            |        |                                |                   |      |  |

| Fixed input level                                                   | VIH    | 3.0                            | ( <sup>*1</sup> ) | V    |  |

| (VDD-dependent input level)                                         |        | (0.7 VDD)                      | ( <sup>*1</sup> ) |      |  |

| Schmitt trigger input                                               |        |                                |                   |      |  |

| Fixed input level                                                   | Vhys   | n/a                            | n/a               | V    |  |

| (VDD-dependent input level)                                         |        | (n/a)                          | (n/a)             |      |  |

| Spike noise width to be rejected by the input filter                | tSP    | n/a                            | n/a               | ns   |  |

| Low level output voltage (open drain or open collector)             |        |                                |                   |      |  |

| (When sinking current is 3 mA.)                                     | VOL1   | 0                              | 0.4               | V    |  |

| (When sinking current is 6 mA.)                                     | (VOL2) | (n/a)                          | (n/a)             |      |  |

| VIH min to LIL max fall time when the BUS line capacitance is       |        |                                |                   |      |  |

| from 10 pF to 400 pF                                                | 40F    |                                |                   |      |  |

| (At VOL1, when the sinking current is 3 mA.)                        | tOF    | —                              | 250 <sup>*2</sup> | ns   |  |

| (At VOL2, when the sinking current is 6 mA.)                        |        | (n/a)                          | (n/a)             | L    |  |

| I/O pin input current when the input voltage is from 0.4 V to 0.9 V | li     | -10                            | 10                | μA   |  |

| I/O pin capacitance                                                 | Ci     |                                | 10                | pF   |  |

n/a: Not applicable.

# (2) I<sup>2</sup>C BUS format (interface protocol)

Write Mode:

|                                                                                  | M                                                                                                                                                      | SB   | B LSE                      |                 | SB LSB                          | N     | ISB   | LSB   |       |

|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------|-----------------|---------------------------------|-------|-------|-------|-------|

|                                                                                  | S                                                                                                                                                      | Slav | e Address                  | Address A Selec |                                 | А     | Data  | А     | Р     |

|                                                                                  | 1 bit                                                                                                                                                  |      | 8 bit 1 bit                |                 | 8 bit                           | 1 bit | 8 bit | 1 bit | 1 bit |

| S:Start condition (start bit recognition)Slave Address:Slave address recognition |                                                                                                                                                        |      |                            |                 |                                 |       |       |       |       |

| A:<br>Slav                                                                       | A:Acknowledge bit (acknowledge recognition)Slave Address:High-side switch and DC/DC comparator on/off control<br>DC/DC comparator frequency adjustment |      |                            |                 |                                 |       |       |       |       |

| Data<br>P:                                                                       | a:                                                                                                                                                     |      | Control and Stop condition | ,               | nent data<br>b bit recognition) |       |       |       |       |

#### Read Mode

|            | M        | SB LSB                         | LSB MSB                                                                                                                           |                              | 5     |       |  |  |  |  |

|------------|----------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------|-------|--|--|--|--|

|            | S        | Slave Address                  | А                                                                                                                                 | Data                         | А     | Р     |  |  |  |  |

|            | 1 bit    | 8 bit                          | 1 bit                                                                                                                             | 8 bit                        | 1 bit | 8 bit |  |  |  |  |

| S:<br>Slav | ve Addro |                                | ``                                                                                                                                | rt bit recogniti<br>ognition | on)   |       |  |  |  |  |

| A:<br>Slav | ve Addr  | ess: Short protec              | Acknowledge bit (acknowledge recognition)<br>Short protection detection (SCP)<br>Overvoltage detection and undervoltage detection |                              |       |       |  |  |  |  |

| Data<br>P: | a:       | Detection da<br>Stop condition |                                                                                                                                   | p bit recogniti              | on)   |       |  |  |  |  |

## (3) Slave Address

| MSB   |    |    |    |    |    |    |    |     |  |  |  |

|-------|----|----|----|----|----|----|----|-----|--|--|--|

|       | A6 | A5 | A4 | A3 | A2 | A1 | A0 | R/W |  |  |  |

| Write | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0   |  |  |  |

| Read  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1   |  |  |  |

The above slave address is registered to Phillips Electronics.

## (4) Select Address

#### Write mode

| Sotting                                 | MSB |    | Select Address |    |    |    |    |    |  |

|-----------------------------------------|-----|----|----------------|----|----|----|----|----|--|

| Setting                                 | A7  | A6 | A5             | A4 | A3 | A2 | A1 | A0 |  |

| Channel on/off control                  | 0   | 0  | 0              | 0  | 0  | 0  | 0  | 0  |  |

| DC/DC comparator<br>frequency variation | 0   | 0  | 0              | 0  | 0  | 0  | 0  | 1  |  |

## Read mode

| Sotting                                       | MSB | Select Address |    |    |    |    |    |    |

|-----------------------------------------------|-----|----------------|----|----|----|----|----|----|

| Setting                                       | A7  | A6             | A5 | A4 | A3 | A2 | A1 | A0 |

| Reduced voltage, overvoltage, short detection | 0   | 0              | 0  | 0  | 0  | 0  | 0  | 0  |

## (5) Detailed data

Write mode

| Cotting                                  | Select  | MSB |    |                            |                               | Data                       |                                          |                            | LSB                           |

|------------------------------------------|---------|-----|----|----------------------------|-------------------------------|----------------------------|------------------------------------------|----------------------------|-------------------------------|

| Setting                                  | Address | A7  | A6 | A5                         | A4                            | A3                         | A2                                       | A1                         | A0                            |

| Channel on/off (1/0)<br>control          | 00HEX   | 0   | 0  | CH1<br>high-side<br>switch | CH1<br>high-side<br>converter | CH1<br>high-side<br>switch | CH1<br>high-side<br>converter            | CH1<br>high-side<br>switch | CH1<br>high-side<br>converter |

| DC/DC comparator<br>frequency adjustment | 01HEX   | 0   | 0  | 0                          | 0                             | 0                          | DC/DC comparator frequency<br>adjustment |                            | equency                       |

#### DC/DC comparator frequency setting

| -            |            |

|--------------|------------|

| Frequency    | Data (hex) |

| Initial      | 00         |

| Initial +10% | 01         |

| Initial +20% | 02         |

| Initial -20% | 03         |

| Initial -10% | 04         |

#### Read mode

| Catting            | Select  | MSB |    | Data |            |            |            |             | LSB          |

|--------------------|---------|-----|----|------|------------|------------|------------|-------------|--------------|

| Setting            | Address | A7  | A6 | A5   | A4         | A3         | A2         | A1          | A0           |

| Reduced voltage,   |         |     |    |      |            |            |            |             |              |

| overvoltage, short |         |     |    |      | SCP signal | SCP signal | SCP signal | Overvoltage | Undervoltage |

| conditions         | 00HEX   | 0   | 0  | 0    | (CH1DC/DC) | (CH2DC/DC) | (CH3DC/DC) | detection   | detection    |

| Channel on/off     |         |     |    |      | comparator | comparator | comparator | signal      | signal       |

| (1/0) condition    |         |     |    |      |            |            |            |             |              |

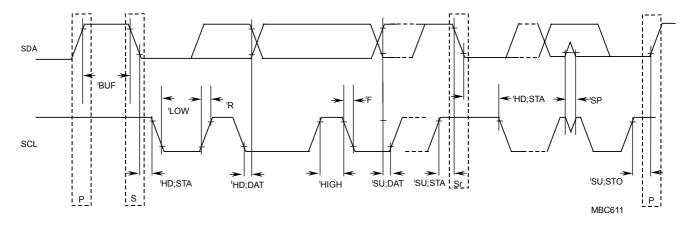

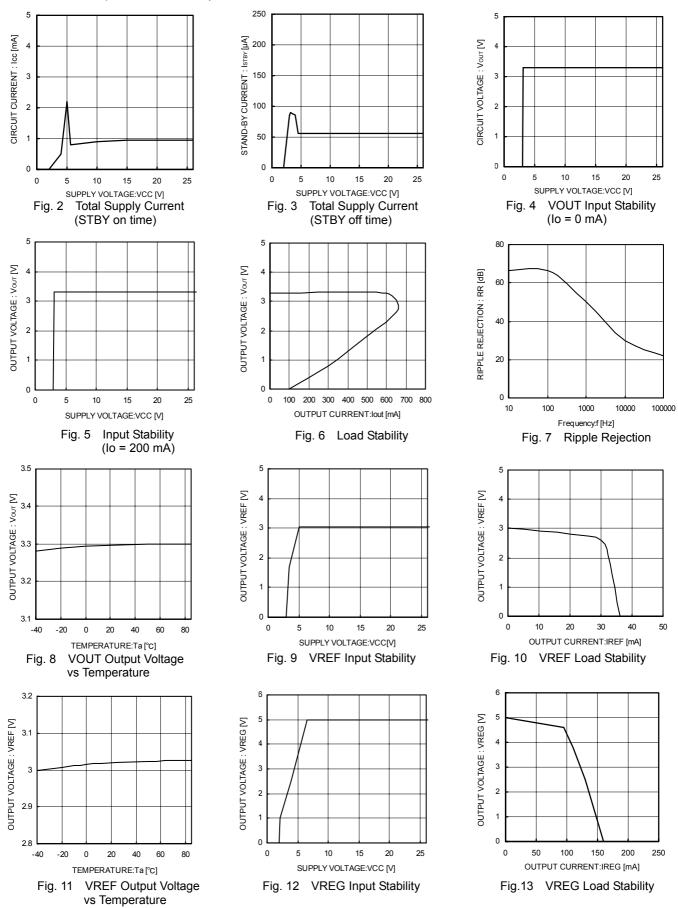

#### ●Reference data (Unless otherwise specified, Ta = 25°C; Vcc = 13.5 V)

Reference data

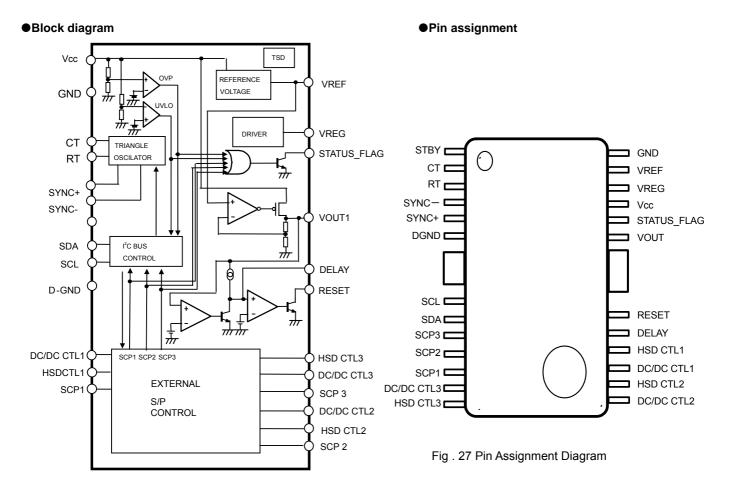

Fig . 26 Block Diagram

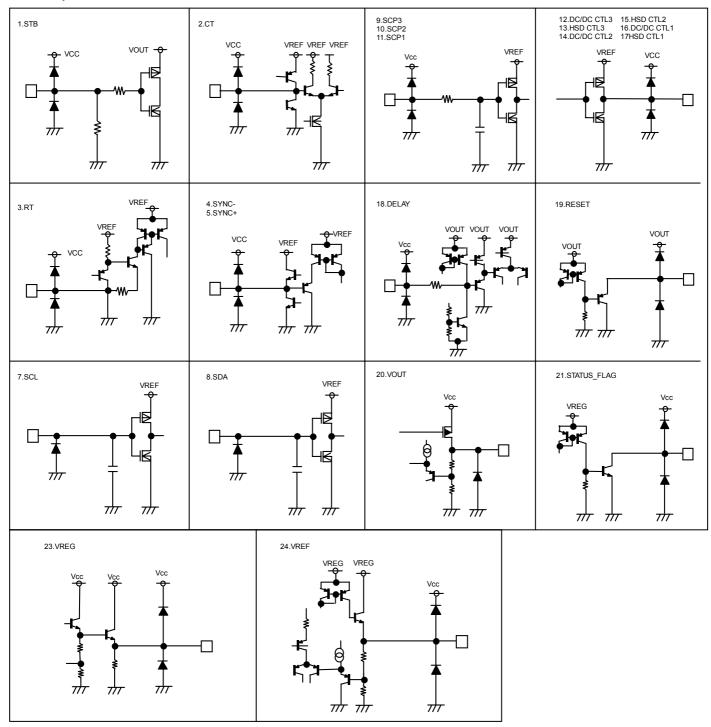

## Pin function descriptions

| lion desci |             |                                                                                         |  |  |  |  |

|------------|-------------|-----------------------------------------------------------------------------------------|--|--|--|--|

| PIN No.    | PIN name    | Function                                                                                |  |  |  |  |

| 1          | STBY        | Standby switch                                                                          |  |  |  |  |

| 2          | СТ          | Used for BD9401/03 DC/DC. Triangular waveform frequency setting capacitor connection pi |  |  |  |  |

| 3          | RT          | Used for BD9401/03 DC/DC. Triangular waveform frequency setting resistance connection   |  |  |  |  |

| 4          | SYNC-       | Triangular waveform inverted output pin                                                 |  |  |  |  |

| 5          | SYNC+       | Triangular waveform non-inverted output pin                                             |  |  |  |  |

| 6          | DGND        | Logic ground                                                                            |  |  |  |  |

| 7          | SCL         | I <sup>2</sup> C BUS clock input pin                                                    |  |  |  |  |

| 8          | SDA         | I <sup>2</sup> C BUS data input pin                                                     |  |  |  |  |

| 9          | SCP3        | Short protection detection input from BD9401/03                                         |  |  |  |  |

| 10         | SCP2        | Short protection detection input from BD9401/03                                         |  |  |  |  |

| 11         | SCP1        | Short protection detection input from BD9401/03                                         |  |  |  |  |

| 12         | DC/DC CTL3  | DC/DC control to BD9401/03                                                              |  |  |  |  |

| 13         | HSD CTL3    | High-side switch control to BD9401/03                                                   |  |  |  |  |

| 14         | DC/DC CTL2  | DC/DC control to BD9401/03                                                              |  |  |  |  |

| 15         | HSD CTL2    | High-side switch control to BD9401/03                                                   |  |  |  |  |

| 16         | DC/DC CTL1  | DC/DC control to BD9401/03                                                              |  |  |  |  |

| 17         | HSD CTL1    | High-side switch control to BD9401/03                                                   |  |  |  |  |

| 18         | DELAY       | Reset delay time setting capacitor connection pin                                       |  |  |  |  |

| 19         | RESET       | RESET output                                                                            |  |  |  |  |

| 20         | VOUT        | Microcontroller regulator output                                                        |  |  |  |  |

| 21         | STATUS_FLAG | OR output for OVP, ULVO, SCP1, SCP2, and SCP3 signals                                   |  |  |  |  |

| 22         | Vcc         | Power supply input pin                                                                  |  |  |  |  |

| 23         | VREG        | BD9401FM/BD9403FV reference voltage output pin (5 V)                                    |  |  |  |  |

| 24         | VREF        | BD9401FM/BD9403FV reference voltage output pin (3 V)                                    |  |  |  |  |

| 25         | GND         | Ground pin                                                                              |  |  |  |  |

| FIN        | FIN         | Heat dissipation fin; connect to ground.                                                |  |  |  |  |

Fig. 28

#### Block operation descriptions

• I<sup>2</sup>C BUS CONTROL/EXTERNAL S/P CONTROL

I<sup>2</sup>C BUS control/external S/P control performs BUS communications control, serial/parallel conversion, and parallel/serial conversion. In write mode, outputs BD9401FM/BD9403FV output on/off control and adjusts the triangular waveform oscillator's frequency.

In read mode, converts switching regulator short protection detection, overvoltage detection, and undervoltage detection information from the BD9401FM/BD9403FV into I<sup>2</sup>C BUS signals.

#### Regulator

Supports the microcontroller regulator, generating output of 3.3 V at a precision of  $\pm 2\%$  and a current capacity of 250 mA. This regulator operates even during standby operation, and low-quiescent current technology delivers a total supply current of 60  $\mu$ A, including RESET and detectors.

#### • RESET

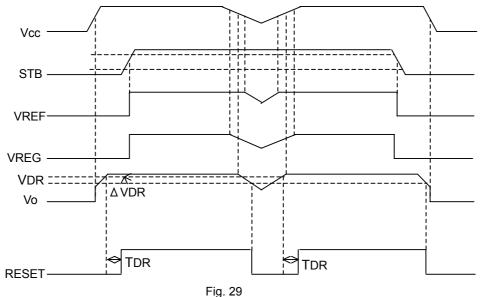

Acts as the VOUT (3.3 V) detection reset circuit. This block's power supply is connected to VOUT, and its operation is linked to VOUT. It uses a detection voltage of 2.80 V (Typ.) and a hysteresis of 90 mV (Typ.). The CT pin capacitor can be used to set the delay time at reset.

• VREF (3.0 V)

The reference voltage circuit for the BD9400BFP's internal I<sup>2</sup>C BUS block and triangular waveform oscillator as well as the BD9401FM/BD9403FV.

It generates output of 3.0 V at a precision of  $\pm$ 1%. Its current capacity is 1 mA.

• VREG (5.0 V)

The reference voltage circuit for the BD9401FM/BD9403FV. The circuit uses 5.7 V emitter follower output, so the output voltage varies with the output current. Its current capacity is 10 mA.

• OVP/UVLO

The overvoltage detection/undervoltage detection circuit, with detection voltages of 18.5 V (Typ.) and 8.5 V (Typ.), and hysteresis values of 400 mA (Typ.) and 150 mV (Typ.). The detection signals are output using the  $I^2C$  BUS read mode.

• OSC

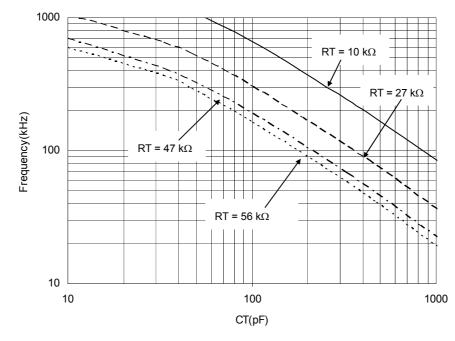

The BD9401/FM/BD9403FV switching regulator's triangular oscillator. The frequency can be set with the CT pin's capacitor and the RT pin's resistor. SYNC+ and SYNC- outputs are inverted 180°.

• STATUS\_FLAG

This flag is set when either OVP/UVLO detection or BD9401FM/BD9403FV short protection is activated. (Its output changes to low.) Uses open collector output with a current capacity of 1 mA. Signal should be pulled up with a resistor.

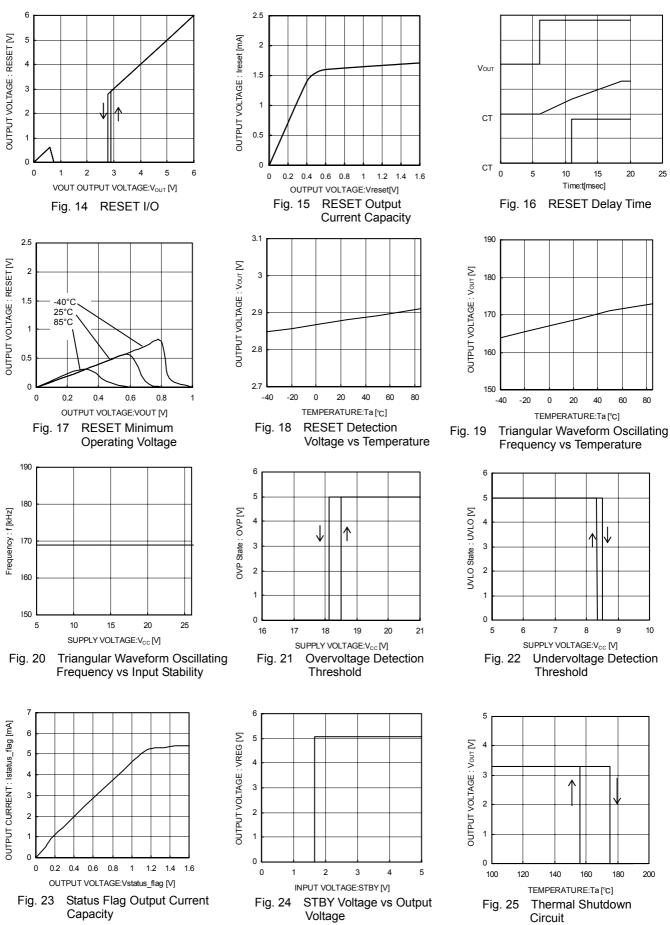

## Timing chart

#### •Selecting application components

#### 1) 3.3 V regulator

• A capacitor used to eliminate oscillation must be inserted between the Vout and GND pins. Variations in the capacitance or ESR, due to temperature variations or other factors, may result in oscillation. It is recommended to use a  $4.7\mu$ F (or higher) ceramic capacitor or an electrolytic capacitor with an ESR of 0.1  $\Omega$  to 5  $\Omega$  to stop oscillation.

#### Protection circuits

Over current protection circuit

The IC incorporates a built-in overcurrent protection circuit that operates according to the output current capacity. This circuit serves to protect the IC from damage when the load is shorted. The protection circuit is designed to limit current flow by not latching in the event of a large and instantaneous current flow originating from a large capacitor or other component. These protection circuits are effective in preventing damage due to sudden and unexpected accidents. However, the IC should not be used in applications characterized by the continuous operation or transitioning of the protection circuits. At the time of thermal designing, keep in mind that the current capability has negative characteristics to temperatures.

#### • Back current when Vcc is shorted

The BD9400BFP does not incorporate a built-in back current protection circuit that operates when Vcc is shorted with the GND pin. To prevent back current, if necessary, a back current prevention diode can be inserted directly into the current flow.

#### 2) RESET

The detection threshold voltage determines the reset triggering point. Regulator output will switch on/off whenever the voltage applied to the input reaches the threshold voltage. A hyst of 50 mV (Typ.) is added to the reset trigger point to eliminate output shudder. The delay time to be implemented when clearing the reset can be set with the CT pin capacitor. An input of 1 V or higher is required for full circuit operation.

#### 3) VREF

Connect a 0.47  $\mu F$  to 10  $\mu F$  capacitor to VREF pin for noise reduction.

#### 4) VREG

Connect a 0.47  $\mu F$  to 10  $\mu F$  capacitor to the VREG pin for noise reduction.

#### 5) OSC

The triangular waveform oscillator frequency is determined with the RT pin's resistor and the CT pin's capacitor. For more information about the RT and CT settings and corresponding frequencies, see Figure 30. Set the RT resistor from 10 k $\Omega$  to 100 k $\Omega$ , and the CT pin's capacitor from 33 pF to 2,200 pF.

#### ●I/O Equivalent circuits

Fig. 31

#### Operation Notes

#### 1. Absolute maximum ratings

Use of the IC in excess of absolute maximum ratings, such as the applied voltage or operating temperature range (Topr), may result in IC damage. Assumptions should not be made regarding the state of the IC (short mode or open mode) when such damage is suffered. A physical safety measure, such as a fuse, should be implemented when using the IC at times where the absolute maximum ratings may be exceeded.

#### 2. GND potential

Ensure a minimum GND pin potential in all operating conditions. Make sure that no pins are at a voltage below the GND at any time, regardless of whether it is a transient signal or not.

#### 3. Thermal design

Perform thermal design, in which there are adequate margins, by taking into account the permissible dissipation (Pd) in actual states of use.

4. Short circuit between terminals and erroneous mounting

Pay attention to the assembly direction of the ICs. Wrong mounting direction or shorts between terminals, GND, or other components on the circuits, can damage the IC.

- Operation in strong electromagnetic field Using the ICs in a strong electromagnetic field can cause operation malfunction.

- 6. Testing on application boards

When testing the IC on an application board, connecting a capacitor to a pin with low impedance subjects the IC to stress. Always discharge capacitors after each process or step. Always turn the IC's power supply off before connecting it to, or removing it from a jig or fixture, during the inspection process. Ground the IC during assembly steps as an antistatic measure. Use similar precaution when transporting and storing the IC.

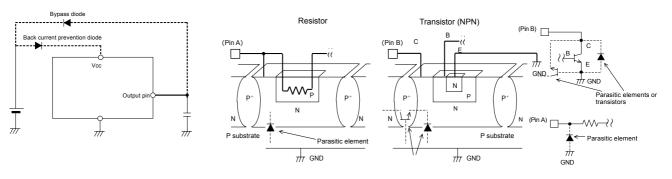

### 7. Regarding input pin of the IC (Fig. 33)

This monolithic IC contains  $P^+$  isolation and P substrate layers between adjacent elements to keep them isolated. P–N junctions are formed at the intersection of these P layers with the N layers of other elements, creating a parasitic diode or transistor. For example, the relation between each potential is as follows:

When GND > Pin A and GND > Pin B, the P–N junction operates as a parasitic diode.

When Pin B > GND > Pin A, the P–N junction operates as a parasitic transistor.

Parasitic diodes can occur inevitably in the structure of the IC. The operation of parasitic diodes can result in mutual interference among circuits, operational faults, or physical damage. Accordingly, methods by which parasitic diodes operate, such as applying a voltage that is lower than the GND (P substrate) voltage to an input pin, should not be used.

8. Ground wiring patterns

The power supply and ground lines must be as short and thick as possible to reduce line impedance. Fluctuating voltage on the power ground line may damage the device.

9. Thermal Shutdown Circuit (TSD)

The IC incorporates a built-in thermal shutdown circuit (TSD circuit). The thermal shutdown circuit (TSD circuit) is designed only to shut the IC off to prevent runaway thermal operation. It is not designed to protect the IC or guarantee its operation. Do not continue to use the IC after operating this circuit or use the IC in an environment where the operation of this circuit is assumed.

#### 10. Over current protection circuit

The IC incorporates a built-in overcurrent protection circuit that operates according to the output current capacity. This circuit serves to protect the IC from damage when the load is shorted. The protection circuit is designed to limit current flow by not latching in the event of a large and instantaneous current flow originating from a large capacitor or other component. These protection circuits are effective in preventing damage due to sudden and unexpected accidents. However, the IC should not be used in applications characterized by the continuous operation or transitioning of the protection circuits. At the time of thermal designing, keep in mind that the current capability has negative characteristics to temperatures.

11. When the Vcc pin is opposite in voltage to each pin in the application, the internal circuit or element may be damaged. For example, such damage might occur when Vcc is shorted with the GND pin while an external capacitor is charged. Use the output pin capacity with a maximum capacitance of 1000 μF. It is recommended to insert a diode in order to prevent back current flow in series with Vcc or bypass diodes between Vcc and each pin.

Fig . 32 Bypass diode

Fig. 33 Example of Simple Bipolar IC Architecture

#### Power dissipation reduction

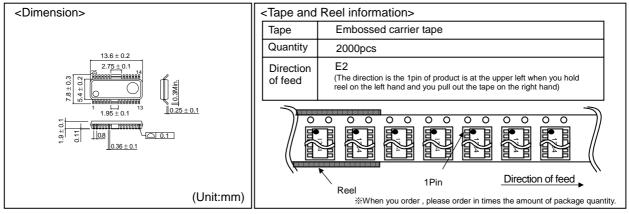

## HSOP25

- The contents described herein are correct as of April, 2006

- The contents described herein are subject to change without notice. For updates of the latest information, please contact and confirm with ROHM CO. LTD.

fuel controllers and other safety devices), please be sure to consult with our sales representative in advance.

- Any part of this application note must not be duplicated or copied without our permission.

- Application circuit diagrams and circuit constants contained herein are shown as examples of standard use and operation. Please pay careful attention to the peripheral conditions when designing circuits and deciding upon circuit constants in the set. Any data, including, but not limited to application circuit diagrams and information, described herein are intended only as illustrations of such devices and not as the specifications for such devices. ROHM CO.LTD. disclaims any

- warranty that any use of such devices shall be free from infringement of any third party's intellectual property rights or other proprietary rights, and further, assumes no liability of whatsoever nature in the event of any such infringement, or arising from or connected with or related to the use of such devices.

- Upon the sale of any such devices, other than for buyer's right to use such devices itself, resel or otherwise dispose of the same, implied right or license to practice or commercially exploit any intellectual property rights or other proprietary rights owned or controlled by ROHM CO., LTD. is granted to any such buyer.

- The products described herein utilize silicon as the main material.

The products described herein are not designed to be X ray proof.

The products listed in this catalog are designed to be used with ordinary electronic equipment or devices (such as audio visual equipment, office-automation equipment, communications devices, electrical appliances and electronic toys). Should you intend to use these products with equipment or devices which require an extremely high level of reliability and the malfunction of which would directly endanger human life (such as medical instruments, transportation equipment, aerospace machinery, nuclear-reactor controllers,

Excellence in Electronics

## ROHM CO., LTD.

21, Saiin Mizosaki-cho, Ukyo-ku, Kyoto 615-8585, Japan TEL: (075)311-2121 FAX: (075)315-0172 URL http://www.rohm.com

Published by LSI Application Engineering Dept. Contact us for further information about the products.

Contact us for further information about th Atlanta U.S.A. /ROHM ELECTRONICS ATLANTA SALES OFFICE (DIVISION OF ROHM ELE.U.S.A., LLC)) TEL:+1(770)754-5972 FAX:+1(770)754-0901 Dellas U.S.A. /ROHM ELECTRONICS DALLAS SALES OFFICE (DIVISION OF ROHM ELE.U.S.A., LLC)) TEL:+1(972)312-8818 FAX:+1(972)312-0330 San Diego U.S.A. /ROHM ELECTRONICS SAN DIEGO SALES OFFICE (DIVISION OF ROHM ELE.U.S.A., LLC) TEL:+1(858)825-3630 FAX:+1(858)825-3670 Germany / ROHM ELECTRONICS CMBH (URN) TEL:+48(2154)9210 FAX:+449(2154)921400 United Kingdom / ROHM ELECTRONICS CMBH (URN) TEL:+449(2154)9210 FAX:+449(2154)921400 United Kingdom / ROHM ELECTRONICS CMBH (URN) TEL:+449(2154)9210 FAX:+449(2154)921400 United Kingdom /ROHM ELECTRONICS CMBH (URN) TEL:+43(2190-2307500 FAX:+439(21954)75-8971 TEL:+43(219740622 FAX:+4362(21957-8971) Shanghai China / ROHM ELECTRONICS (HAX) CO, LTD. TEL:+852(2170622 FAX:+4562(21957-8971) Shanghai AroHM ELECTRONICS (HAANCHAI) CO, LTD. TEL:+80(411)8230-8549 FAX:+86(21)8247-2066

CIS.

Beijing China / BEIJING REPRESENTATIVE OFFICE TEL:+80(10)8525-2483

Taiwan / ROHM ELECTRONICS TAIWAN CO., LTD. TEL:+80(2)2500-8056

TEM:=80(2)2500-8056

FAX:=80(2)2500-8056

FAX:=80(2)2500-8056

FAX:=80(2)2500-8056

FAX:=80(2)2800-8056

FAX:=80(2)2800-8076

FAX:=80(2)280-8076

FAX:=80(2)280-8034

#### Notes

- No technical content pages of this document may be reproduced in any form or transmitted by any means without prior permission of ROHM CO.,LTD.

- The contents described herein are subject to change without notice. The specifications for the

product described in this document are for reference only. Upon actual use, therefore, please request

that specifications to be separately delivered.

- Application circuit diagrams and circuit constants contained herein are shown as examples of standard use and operation. Please pay careful attention to the peripheral conditions when designing circuits and deciding upon circuit constants in the set.

- Any data, including, but not limited to application circuit diagrams information, described herein are intended only as illustrations of such devices and not as the specifications for such devices. ROHM CO.,LTD. disclaims any warranty that any use of such devices shall be free from infringement of any third party's intellectual property rights or other proprietary rights, and further, assumes no liability of whatsoever nature in the event of any such infringement, or arising from or connected with or related to the use of such devices.

- Upon the sale of any such devices, other than for buyer's right to use such devices itself, resell or

otherwise dispose of the same, no express or implied right or license to practice or commercially

exploit any intellectual property rights or other proprietary rights owned or controlled by

- ROHM CO., LTD. is granted to any such buyer.

- Products listed in this document are no antiradiation design.

The products listed in this document are designed to be used with ordinary electronic equipment or devices (such as audio visual equipment, office-automation equipment, communications devices, electrical appliances and electronic toys).

Should you intend to use these products with equipment or devices which require an extremely high level of reliability and the malfunction of which would directly endanger human life (such as medical instruments, transportation equipment, aerospace machinery, nuclear-reactor controllers, fuel controllers and other safety devices), please be sure to consult with our sales representative in advance.

It is our top priority to supply products with the utmost quality and reliability. However, there is always a chance of failure due to unexpected factors. Therefore, please take into account the derating characteristics and allow for sufficient safety features, such as extra margin, anti-flammability, and fail-safe measures when designing in order to prevent possible accidents that may result in bodily harm or fire caused by component failure. ROHM cannot be held responsible for any damages arising from the use of the products under conditions out of the range of the specifications or due to non-compliance with the NOTES specified in this catalog.

Thank you for your accessing to ROHM product informations. More detail product informations and catalogs are available, please contact your nearest sales office.

# **ROHM** Customer Support System

THE AMERICAS / EUROPE / ASIA / JAPAN

## www.rohm.com

Contact us : webmaster@rohm.co.jp

Copyright © 2008 ROHM CO.,LTD. ROHM CO., LTD. 21 Saiin Mizosaki-cho, Ukyo-ku, Kyoto 615-8585, Japan TEL : +81-75-311-2121 FAX : +81-75-315-0172

Appendix1-Rev2.0

rohm